- 您现在的位置:买卖IC网 > Sheet目录2000 > ISD5008EYI (Nuvoton Technology Corporation of America)IC VOICE REC/PLAY 4-8MIN 28-TSOP

ISD5008

Publication Release Date: Oct 31 2008

- 11 -

Revision 1.2

6.1.5

Memory Architecture

The ISD5008 device contains a total of 1,920K Flash memory cells, which is organized as 1,200 rows

of 1,600 cells each. The duration is counted according to the number of rows, while the row number is

represented by the related 16 address bits of MOSI as described in the SPI section.

6.1.6

Programming

The ISD5008 device is also ideal for playback-only applications, where single- or multiple-message

playback is controlled through the SPI port. Once the desired message configuration is created,

duplicates can easily be generated via a third-party programmer. For more information on available

application tools and programmers, please see the Nuvoton website at www.Nuvoton-usa.com.

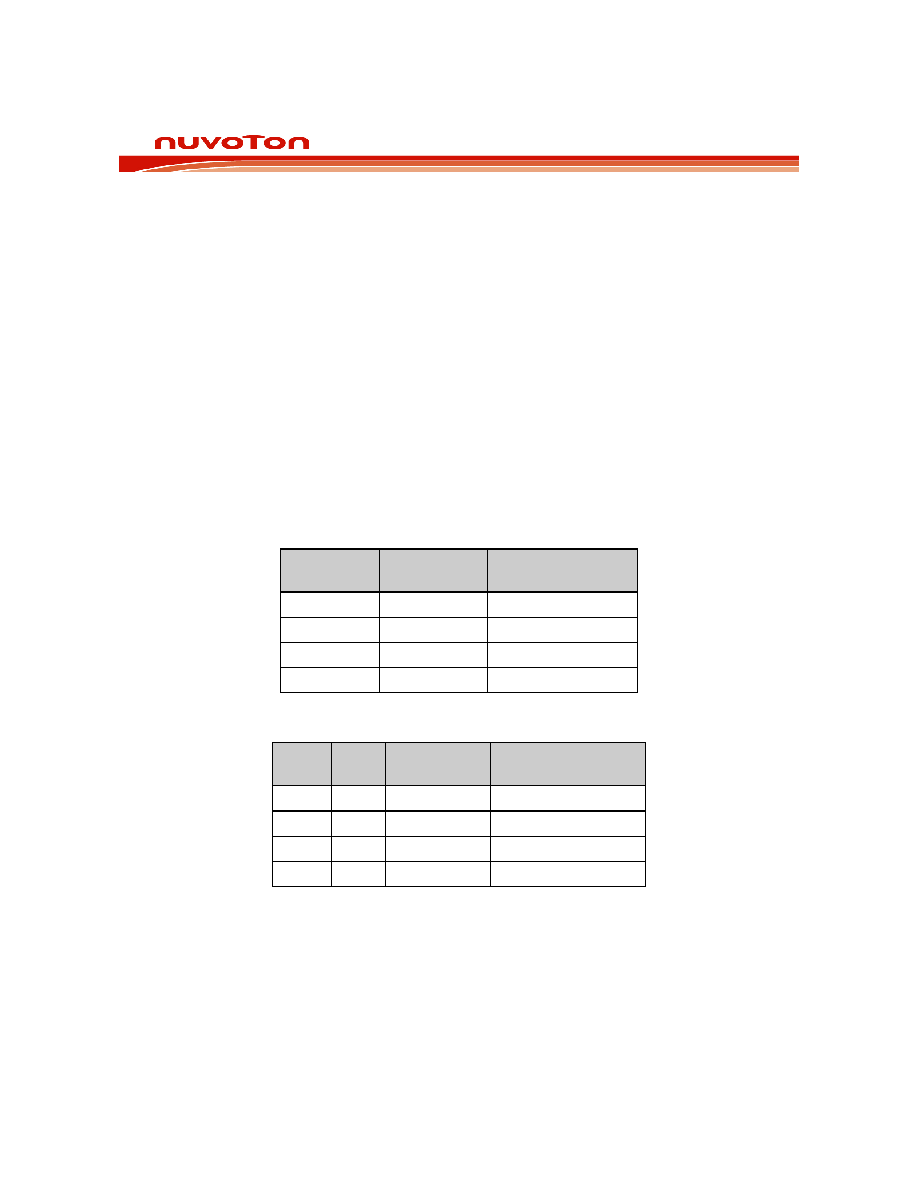

TABLE 2: EXTERNAL CLOCK INPUT

Duration

(Minutes)

Sample Rate

(kHz)

Required Clock

(kHz)

4

8.0

1024

5

6.4

819.2

6

5.3

682.7

8

4.0

512

TABLE 3: INTERNAL SAMPLING RATE / FILTER EDGE

FLD1

FLD0

Sample

Rate (kHz)

Filter Pass Band

(kHz)

0

8

3.4

0

1

6.4

2.7

1

0

5.3

2.3

1

4

1.7

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

ISL12008IB8Z

IC RTC I2C LO-POWER 8-SOIC

ISL12020MIRZ-T7A

IC RTC/CALENDAR TEMP SNSR 20DFN

ISL12022IBZ-T7A

IC RTC/CALENDAR TEMP SNSR 8SOIC

ISL12022MAIBZ

IC RTC/CALENDAR TEMP SNSR 20SOIC

ISL12022MIBZ-T7A

IC RTC/CALENDAR TEMP SNSR 20SOIC

ISL12022MIBZR5421

IC RTC/CALENDAR TEMP SNSR 20SOIC

ISL12023IVZ

IC RTC/CLDR TEMP SNSR 14-TSSOP

ISL12024IRTCZ

IC RTC/CALENDER 64BIT 8-TDFN

相关代理商/技术参数

ISD5008P

功能描述:IC VOICE REC/PLAY 4-8MIN 28-DIP RoHS:否 类别:集成电路 (IC) >> 接口 - 语音录制和重放 系列:ISD5008 标准包装:14 系列:- 接口:串行 滤波器通频带:1.7kHz 持续时间:8 ~ 32 秒 安装类型:通孔 封装/外壳:28-DIP(0.300",7.62mm) 供应商设备封装:28-PDIP 其它名称:90-21300+000

ISD5008PY

功能描述:IC VOICE REC/PLAY 4-8MIN 28-DIP RoHS:是 类别:集成电路 (IC) >> 接口 - 语音录制和重放 系列:ISD5008 标准包装:14 系列:- 接口:串行 滤波器通频带:1.7kHz 持续时间:8 ~ 32 秒 安装类型:通孔 封装/外壳:28-DIP(0.300",7.62mm) 供应商设备封装:28-PDIP 其它名称:90-21300+000

ISD5008S

功能描述:IC VOICE REC/PLAY 4-8MIN 28-SOIC RoHS:否 类别:集成电路 (IC) >> 接口 - 语音录制和重放 系列:ISD5008 标准包装:14 系列:- 接口:串行 滤波器通频带:1.7kHz 持续时间:8 ~ 32 秒 安装类型:通孔 封装/外壳:28-DIP(0.300",7.62mm) 供应商设备封装:28-PDIP 其它名称:90-21300+000

ISD5008SD

制造商:未知厂家 制造商全称:未知厂家 功能描述:SINGLE CHIP VOICE RECORD PLAYBACK DEVICE 4-, 5-, 6-, AND 8- MINUTE DURATIONS

ISD5008SERIES

制造商:未知厂家 制造商全称:未知厂家 功能描述:Single-Chip Voice Record/Playback Device

ISD5008SI

功能描述:IC VOICE REC/PL 4-8MIN IN 28SOIC RoHS:否 类别:集成电路 (IC) >> 接口 - 语音录制和重放 系列:ISD5008 标准包装:14 系列:- 接口:串行 滤波器通频带:1.7kHz 持续时间:8 ~ 32 秒 安装类型:通孔 封装/外壳:28-DIP(0.300",7.62mm) 供应商设备封装:28-PDIP 其它名称:90-21300+000

ISD5008SIR

功能描述:IC VOICE REC/PL 4-8MIN IN 28SOIC RoHS:否 类别:集成电路 (IC) >> 接口 - 语音录制和重放 系列:ISD5008 标准包装:14 系列:- 接口:串行 滤波器通频带:1.7kHz 持续时间:8 ~ 32 秒 安装类型:通孔 封装/外壳:28-DIP(0.300",7.62mm) 供应商设备封装:28-PDIP 其它名称:90-21300+000

ISD5008SY

功能描述:IC VOICE REC/PLAY 4-8MIN 28-SOIC RoHS:是 类别:集成电路 (IC) >> 接口 - 语音录制和重放 系列:ISD5008 标准包装:14 系列:- 接口:串行 滤波器通频带:1.7kHz 持续时间:8 ~ 32 秒 安装类型:通孔 封装/外壳:28-DIP(0.300",7.62mm) 供应商设备封装:28-PDIP 其它名称:90-21300+000